The RISC-V corner

What is RISC-V?

RISC-V (pronounced “risk-five”) is an open instruction set architecture (ISA) based on established reduced instruction set computing (RISC) principles.

RISC-V (pronounced “risk-five”) is an open instruction set architecture (ISA) based on established reduced instruction set computing (RISC) principles.

RISC-V is governed by the non-profit RISC-V foundation and it’s member companies after being originally developed at the University of California, Berkeley. SiFive, a significant contributor to the RISC-V foundation, manufactured the first commercially available RISC-V SoC, the Freedom E310.

RISC-V is governed by the non-profit RISC-V foundation and it’s member companies after being originally developed at the University of California, Berkeley. SiFive, a significant contributor to the RISC-V foundation, manufactured the first commercially available RISC-V SoC, the Freedom E310.

License

In contrast to most ISAs, the RISC-V ISA can be freely used for any purpose, permitting anyone to design, manufacture and sell RISC-V chips and software. The RISC-V authors aim to provide several CPU designs freely available under a BSD license.

Chips & boards

The GNU MCU Eclipse currently supports the following devices:

- SiFive Freedom E310, RV32IMAC, a 32-bit embedded processor

- SiFive E31 Coreplex, RV32IMAC, a Verilog synthesised 32-bit embedded processor

- SiFive E51 Coreplex, RV64IMAC, a a Verilog synthesised 64-bit embedded processor

The following boards are supported:

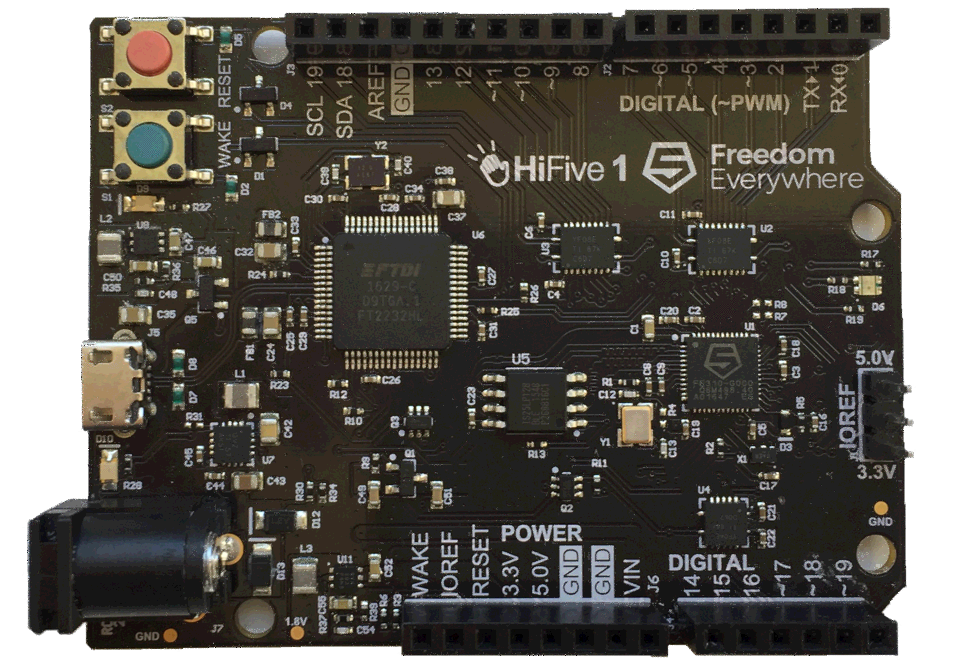

- SiFive HiFive1, an Arduino-compatible development kit featuring the Freedom E310

- Xilinx/Digilent Artix-7 35T Arty FPGA Evaluation Kit, a board capable of running the synthesised E31/E51 devices.

Tips & tricks

- Programmer - programmer info

- Flashing the Arty boards - a solution to reprogram the Arty board without Xilinx Vivado

- Arty JTAG adapter - a solution to connect a standard JTAG ribon cable to an Arty board

- FTDI JTAG drivers - workaround to reconfigure the FTDI as JTAG programmer

Links

Manuals

- The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Document Version 2.2 (read online

- The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version1.10 (read online

- Arty Reference Manual

Downloads

- GNU MCU Eclipse IDE for C/C++ Developers

- GNU MCU Eclipse plug-ins

- GNU MCU Eclipse Windows Build Tools

- xPack GNU RISC-V Embedded GCC

- xPack OpenOCD